Fundamentals of CMOS image sensor(2)

안녕하세요. 이전 포스팅에 이어서 보도록 합시다. 책의 내용과 제가 들었던 강의 내용 등을 정리해서 작성했습니다. 그림은 우선 대략적으로 그려서 깔끔하지는 않네요..

3. basic pixel structures

- 3T-APS 구조

아래 그림은 3T-APS의 구조입니다. 3T APS의 특징은시간에 따라 (source follower)SF의 출력 값이 점차 감소된다는 점입니다.

1. 동작 설명

첫번째, RST가 켜져서 reset SW TR이 켜지게되면 PD의 n영역은 vdd-vth로 충전(reset)된다.

두번째, reset SW TR이 꺼지게 되면 PD는 floating 상태이다. 그럼 이때, 빛이 들어오면 Cpd에 전하가 충전이 됩니다. 그리고 이는 전압으로 나타나지게 된다. 리셋에서는 양의 전압으로 충전되어 있고, 입사된 빛에 의해 생성된 전자로 인해 최종 축적된 전압은 줄어듭니다.

세번째, 픽셀 구조에서는 추가로 word line, bit line에 해당하는 pixel select을 위한 SW TR이 존재합니다. 이때 해당 픽셀의 word line i번째가 켜지면 이 전압이 SF를 거쳐 출력된다.

마지막으로, 다시 reset SW가 켜지면서 충전되고 위과정을 반복함.

2. 이슈

- kTC noise를 줄이기 쉽지 않다(?). 이 부분은 이해가 안갑니다.

- PD가 detect과 conversion을 동시에 하기 때문에 PD design의 제약이 있습니다. 4T-APS 대비 단점입니다.

- Source follower 의 경우, 사이즈가 작으면 변동이 크다?

3. 3T APS에서 CDS(correlated double sampling)를 사용하는 방법

그림을 급하게 그린 것입니다... CDS는 그림에서 출력쪽의 Cos와 Cor의 전압 차이를 이용합니다. 동작으로 보면Signal sampling phase에서는 SS 전압을 켜서 이 TR을 on 시킵니다. 대략적인 수식은 아래와 같습니다.

빛에 의해 생선된 전하량 Q=q*Qsig=C*V -> V= q*Qsig/C

리셋일 때의 전압 : Vd

SF의 Vgs : Vgsf

Vo= Vd-(qQsig/CD)-Vgsf

4.시뮬레이션 모델링하기

이 부분은 제가 idec에서 진행한 CIS 시뮬레이션 강의를 듣고 정리한 것입니다.

시뮬레이션 tool에서 픽셀 회로를 돌려보기 위해서 픽셀모델링이 필요합니다. 위의 그림과 같이 픽셀에 VCCS의 ideal 전류원을 사용하여 모델링 할 수 있습니다. 이는 Reset이 꺼졌을 때, CD의 전압이 빠지도록 해주기 위함입니다.

전류원은 VCCS로 정해서 불러오고, 이 전류원 내용을 'I_VCCS 1 gnd Resetb gnd 1e-11/1.8' 로 해주면 Reset이 꺼질 때마다 Resetb는 1.8V가 되고 이때 10 pA가 흐르게 됩니다.

추가로, CD가 100fF 이고, VD가 1.4V(초기의 VDD-vth)라면, Q= 140fC 이고, integration time(리셋 후 다음 리셋까지의 시간)이 4ms이면, 40fC를 소모합니다.

위의 timming diagram을 보면, reset sampling phase에서는 Reset후 SR 스위치 TR로 출력을 sampling을 합니다. 이후, reset이 꺼지고, photon이 CD에 charge되는 integration time을 부여하고, 이때는 위의 modeling된 VCCS로 VD의 값이 점점 감소하게 됩니다. 다음으로, SS 스위치 TR로 출력을 다시 sampling합니다. 이후 이 두번의 sampling 차이를 빼어 주어 3T APS의 CDS를 시뮬레이션 해볼 수 있습니다.

아마 시간이 된다면 LTspice를 이용한 3T-APS array CIS를 readout 까지 달아서 돌려보는 것을 포스팅하도록 하겠습니다.

*full-well capacity와 conversion gain

full-well capacity : PD에 축적될수 있는 전하의 수. 이 값이 크면 그만큼 dynamic range(DR)가 크다. DR=20log(Vmax/Vmin)

conversion gain : 전하 1개가 전압으로 바뀌는 gain. 1/Cpd 로 나타낼 수 있다.

full-well capacity는 Cpd가 커지면 증가합니다. 반면에 Cpd가 커진만큼 이를 전압으로 변환하면 그 값은 더 낮아지게 되므로, 반비례합니다.

앞으로 말할 4T-APS에서는 이 trade-off 관계를 해결하고 kTC노이즈도 개선할 수 있게 됩니다.

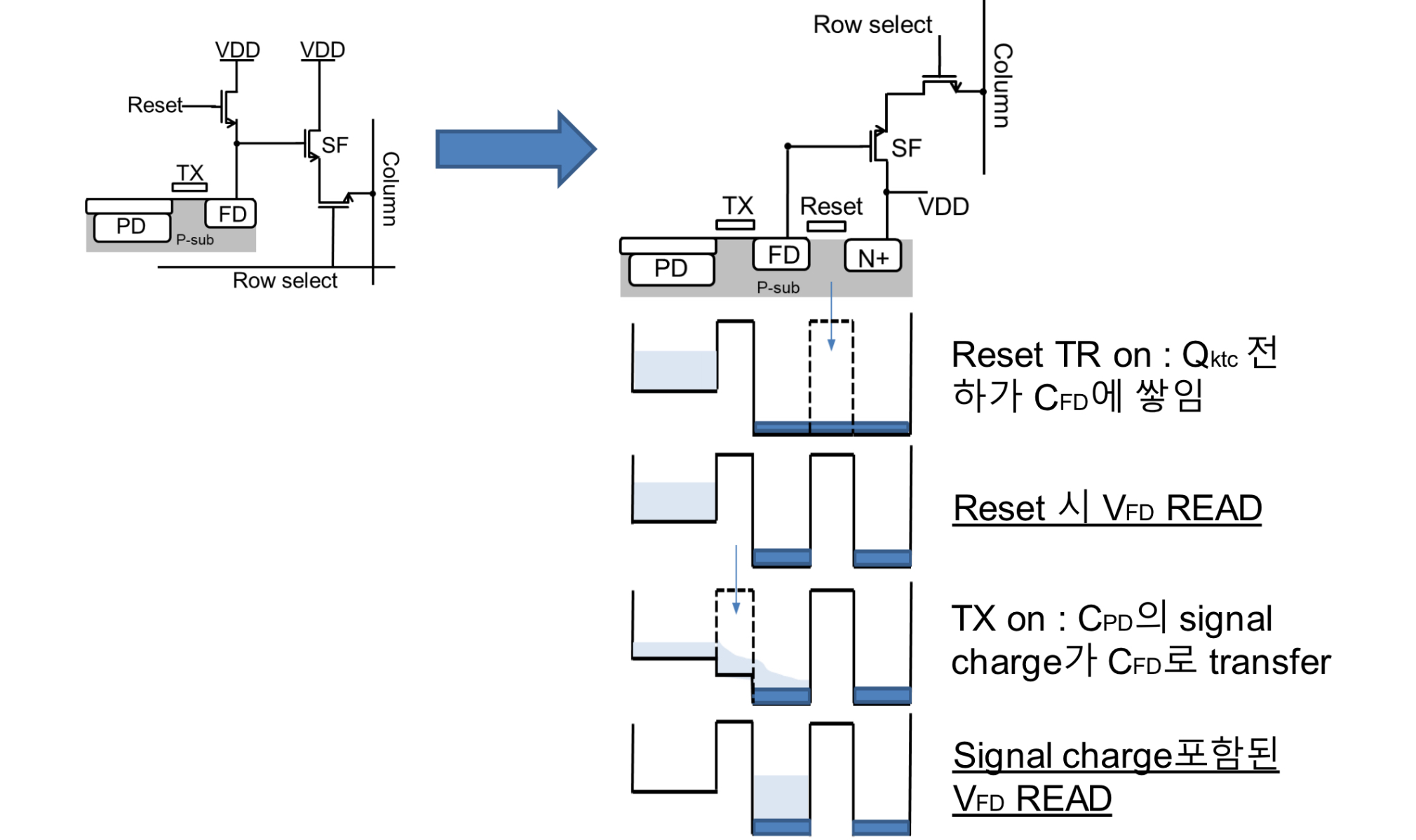

- 4T-APS

우선, 위 그림이 간략하게 구조를 그린 것입니다. 4T-APS의 경우, photodetection과 photoconversion 부분이 분리되어 있습니다. 중간에 TG 스위치가 그 역할입니다. TG가 켜짐으로 PD 전하가 TG의 source 쪽으로 이동하는데 이 부분을 floating diffusion(FD)라 부르겠습니다.

1. 동작 설명

첫번째, signal이 PD에 축적됩니다. 맨 처음 초기상태는 이 PD에 전하가 축적되어 있지 않습니다.

두번째, 이 상태에서 reset SW가 켜져 FD가 reset전압으로 충전됩니다. 이후 CDS를 적용하기 위해서 이때 reset 값도 SEL TR을 on 시켜 읽고 저장해놓습니다(reset readout).

세번째, 이제 그동안 입사된 빛에 의해 PD에 축적된 signal을 TG SW를 켬으로 인해 FD로 옮겨지도록 합니다.

네번째, 다시 SEL TR을 on시켜 읽어드립니다(signal readout).

마지막으로, 위 과정을 반복합니다.

위 그림은 동작에 대한 timimg diagram을 제 나름대로 정리해보았습니다. 그림 마지막에서 보듯이 reset도 readout 시켜 저장하고, signal도 readout후 저장합니다. 이후 이 둘의 연산을 통해 kTC 노이즈를 제거한 온전한 신호값을 출력으로 얻을 수 있습니다.

2. 이슈

reset 전하는 signal 전하를 읽고 난 뒤에 읽을 수 있습니다. 이 두 신호의 차이로 인해 kTC noise를 줄일 수 있습니다.

- 추가적인 TR 필요

- PD에 축적된 신호 전하가 FD로 완전히 옮겨가야 하기 때문에 image lag가 발생할 수 있음.

책에 나온 픽셀에 대한 내용 정리를 마무리 하도록 하겠습니다. 추가로 공부한 내용들은 계속해서 수정해서 업데이트 할 계획입니다. 다음에는 SF포함 readout 회로에 대한 내용입니다.

감사합니다.